ARM7ن½“系结و„

Update-Time : 2011ه¹´2وœˆ24و—¥وکںوœںه››

ن¸€ï¼ژهکه‚¨ه™¨çڑ„ه—ن¸ژهچٹه—

1.ن»ژهپ¶و•°هœ°ه€ه¼€ه§‹çڑ„è؟ç»çڑ„ن¸¤ن¸ھه—èٹ‚و„وˆگن¸€ن¸ھهچٹه—م€‚

2.能被4و•´é™¤çڑ„هœ°ه€çڑ„è؟ç»4ن¸ھه—éک¶و„وˆگن¸€ن¸ھه—

ARMوŒ‡ن»¤çڑ„é•؟ه؛¦هˆڑه¥½وک¯ن¸€ن¸ھه—,ThumbوŒ‡ن»¤çڑ„é•؟ه؛¦هˆڑه¥½وک¯ن¸€ن¸ھهچٹه—

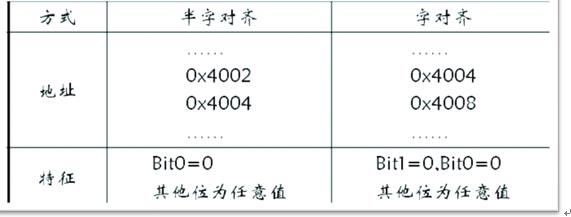

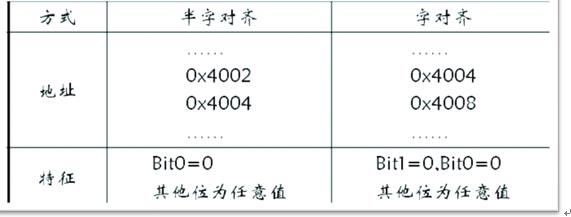

ن؛Œï¼ژهکه‚¨ه™¨çڑ„هکه‚¨و–¹ه¼ڈ(هچٹه—ه¯¹é½گ,ه—ه¯¹é½گ)

1.هچٹه—ه¯¹é½گï¼ڑهکو”¾ن¸€ن¸ھو•°وچ®çڑ„هœ°ه€ه¦‚وœèƒ½è¢«ن؛Œو•´é™¤ï¼Œهˆ™ه®ƒوک¯هچٹه—ه¯¹é½گم€‚هڈچن¹‹ï¼Œهˆ™وک¯éهچٹه—ه¯¹é½گم€‚

2.ه—ه¯¹é½گï¼ڑهکو”¾ن¸€ن¸ھو•°وچ®çڑ„هœ°ه€ه¦‚وœèƒ½è¢«ه››و•´é™¤ï¼Œهˆ™ه®ƒوک¯ه—ه¯¹é½گم€‚هگ¦هˆ™ï¼Œه®ƒوک¯éه—ه¯¹é½گم€‚

ن¸‰ï¼ژARMه¤„çگ†ه™¨çٹ¶و€پï¼ڑ

ARMوœ‰ن¸¤ç§چه¤„çگ†ه™¨çٹ¶و€پï¼ڑARMçٹ¶و€پ,Thumbçٹ¶و€پم€‚

1. ARMçٹ¶و€پï¼ڑ32ن½چم€‚ه¤„çگ†ه™¨و‰§è،Œه—و–¹ه¼ڈçڑ„ARMوŒ‡ن»¤م€‚

2. Thumbçٹ¶و€پï¼ڑ16ن½چم€‚ه¤„çگ†ه™¨و‰§è،Œهچٹه—و–¹ه¼ڈçڑ„ThumbوŒ‡ن»¤م€‚

و³¨ï¼ڑن¸¤ن¸ھçٹ¶و€پن¹‹é—´çڑ„هˆ‡وچ¢وک¯ن¸چن¼ڑه½±ه“چه¤„çگ†ه™¨çڑ„و¨،ه¼ڈوˆ–ه¯„هکه™¨çڑ„ه†…ه®¹م€‚

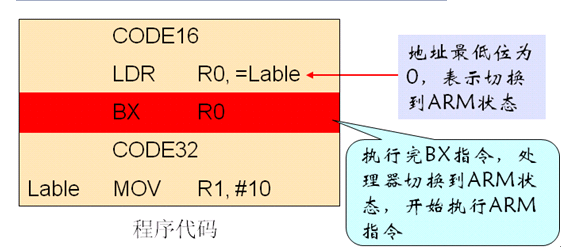

ه®ƒن»¬ن¹‹é—´وک¯ه¦‚ن½•è؟›è،Œهˆ‡وچ¢çڑ„م€‚

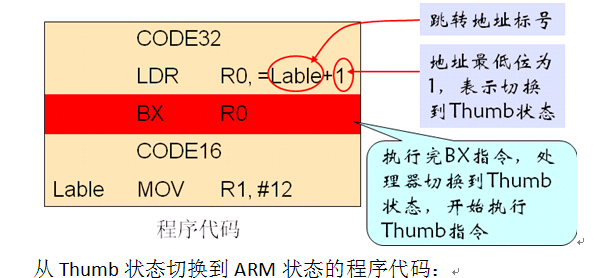

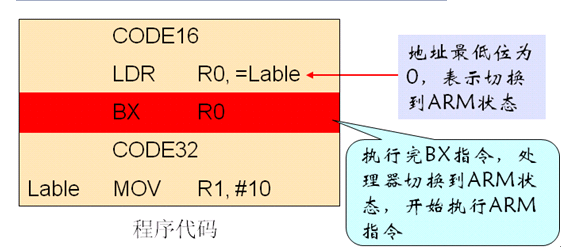

ن½؟用BXوŒ‡ن»¤هœ¨ARMه’ŒThumbçٹ¶و€پن¹‹é—´è؟›è،Œهˆ‡وچ¢م€‚

(ن½†وک¯ï¼Œو‰€وœ‰çڑ„ه¼‚ه¸¸ه¤„çگ†éƒ½وک¯هœ¨ARMçٹ¶و€پن¸و‰§è،Œم€‚ه¦‚وœه¼‚ه¸¸هڈ‘ç”ںهœ¨Thumbçٹ¶و€پن¸ï¼Œه¤„çگ†ه™¨ن¼ڑهˆ‡وچ¢هˆ°ARMçٹ¶و€پم€‚هœ¨ه¼‚ه¸¸ه¤„çگ†è؟”ه›و—¶ï¼Œè‡ھهٹ¨هˆ‡وچ¢ه›Thumbçٹ¶و€پم€‚)

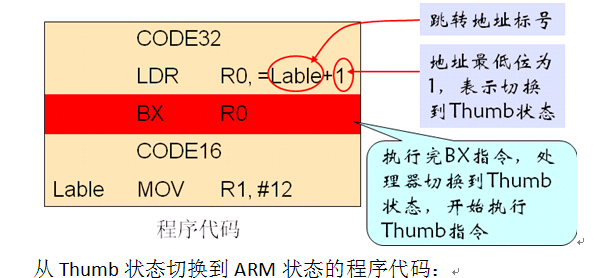

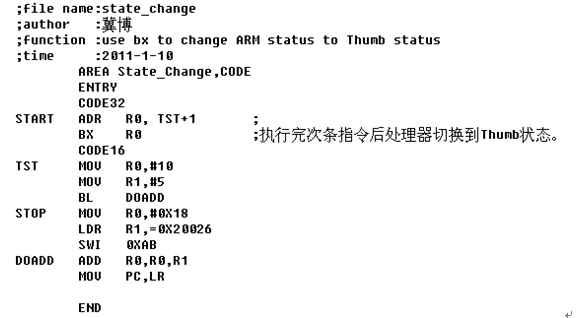

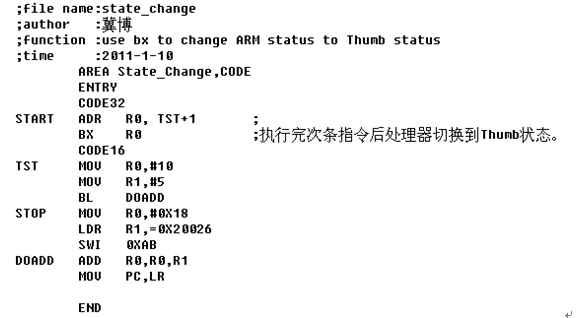

ن»ژARMçٹ¶و€پهˆ‡وچ¢هˆ°Thumbçٹ¶و€پçڑ„程ه؛ڈن»£ç پï¼ڑ

ه…·ن½“程ه؛ڈو¥è¯´وکژه¤„çگ†ه™¨çٹ¶و€پï¼ڑ

程ه؛ڈ1ï¼ڑ

ADR R0,TST+1

و³¨ï¼ڑن¼ھوŒ‡ن»¤ADRه°†ه¯„هکه™¨ه†…ه®¹çڑ„هœ°ه€هکه…¥ه¯„هکه™¨ن¸م€‚è؟™é‡Œه°†هœ°ه€TST+1هکه…¥R0ن¸ï¼Œè؟™و ·ه°±هٹ è½½ن؛†è½¬ç§»هœ°ه€ه¹¶ن¸”设置ن؛†وœ€è؟‘وœ‰و•ˆن½چم€‚

BX R0

و³¨ï¼ڑو¤و—¶ï¼ŒR0ن¸و•°ه€¼çڑ„第0ن½چوک¯1,و‰€ن»¥è¯¥è¯هڈ¥و‰§è،Œه®Œه¤„çگ†ه™¨هˆ‡وچ¢è؟›ه…¥Thumbçٹ¶و€پ,ه¼€ه§‹و‰§è،ŒThumbوŒ‡ن»¤

(وˆ‘ن»¬هڈ¯ن»¥هœ¨AXDن¸‹çœ‹هˆ°و¤و—¶çٹ¶و€په¯„هکه™¨çڑ„Tن½چ被置1.)

CODE16

و³¨ï¼ڑ

Aو±‡ç¼–ه™¨éœ€è¦پçں¥éپ“ن»€ن¹ˆو—¶ه€™ن؛§ç”ںARMن»£ç پ,ن»€ن¹ˆو—¶ه€™ن؛§ç”ںThumb ن»£ç پم€‚

Bن¼ھوŒ‡ن»¤CODE16ه®ڑن¹‰ن¸€ن¸‹çڑ„程ه؛ڈ被编译وˆگThumbو¨،ه¼ڈ,هچ³هگژé¢çڑ„ه°±وک¯16ن½چçڑ„ThumbوŒ‡ن»¤ن؛†م€‚

C.ن¼ھوŒ‡ن»¤CODE32ه®ڑن¹‰ن¸€ن¸‹çڑ„程ه؛ڈه°†è¢«ç¼–译وˆگARMو¨،ه¼ڈ,هچ³هگژé¢çڑ„ه°±وک¯32ن½چçڑ„ARMوŒ‡ن»¤م€‚

Dن¼ھوŒ‡ن»¤CODE16ه’ŒCODE32هڈھوک¯وŒ‡ç¤؛و±‡ç¼–ه™¨هگژé¢وŒ‡ن»¤çڑ„ç±»ه‹ï¼Œه¹¶ن¸چن؛§ç”ںن»»ن½•ن»£ç پ,ن¹ںن¸چè؟›è،Œç¨‹ه؛ڈçٹ¶و€پçڑ„هˆ‡وچ¢م€‚

程ه؛ڈ2ï¼ڑ

و³¨ï¼ڑ

هœ¨Thumbçٹ¶و€پن¸‹ï¼Œè°ƒç”¨è½¯ن¸و–:SWI 0XAB

هœ¨ ARM çٹ¶و€پن¸‹ï¼Œè°ƒç”¨è½¯ن¸و–:SWI 0X123456

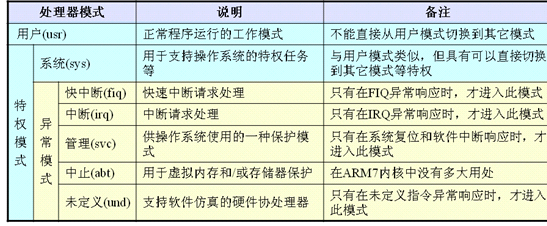

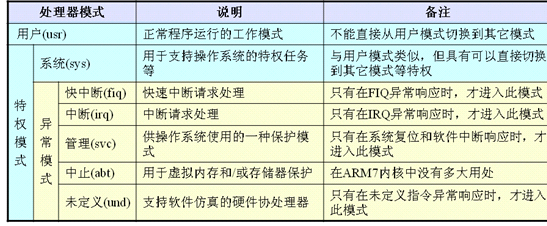

ه››ï¼ژARMه¤„çگ†ه™¨و¨،ه¼ڈï¼ڑ

ARMن½“系结و„و”¯وŒپ7ن¸ه¤„çگ†ه™¨و¨،ه¼ڈï¼ڑ用وˆ·و¨،ه¼ڈ,ه؟«ن¸و–و¨،ه¼ڈ,ن¸و–و¨،ه¼ڈ,ç®،çگ†و¨،ه¼ڈ,ن¸و¢و¨،ه¼ڈ,وœھه®ڑن¹‰و¨،ه¼ڈه’Œç³»ç»ںو¨،ه¼ڈم€‚

1.ه؟«ن¸و–و¨،ه¼ڈ,ن¸و–و¨،ه¼ڈ,ç®،çگ†و¨،ه¼ڈ,ن¸و¢و¨،ه¼ڈه’Œوœھه®ڑن¹‰و¨،ه¼ڈم€‚ه®ƒن»¬ç§°ن¸؛ه¼‚ه¸¸و¨،ه¼ڈم€‚

A.ه¼‚ه¸¸و¨،ه¼ڈو—¢هڈ¯ن»¥é€ڑè؟‡ç¨‹ه؛ڈهˆ‡وچ¢è؟›ه…¥ه¤–,ن¹ںهڈ¯ن»¥وœ‰ç‰¹ه®ڑçڑ„ه¼‚ه¸¸è؟›ه…¥م€‚

B.ه½“特ه®ڑçڑ„ه¼‚ه¸¸ه‡؛çژ°و—¶ï¼Œه¤„çگ†ه™¨è؟›ه…¥ç›¸ه؛”é¥؟و¨،ه¼ڈم€‚و¯ڈç§چو¨،ه¼ڈ都وœ‰وںگن؛›é™„هٹ çڑ„ه¯„هکه™¨م€‚

2.ç³»ç»ںو¨،ه¼ڈه’Œç”¨وˆ·و¨،ه¼ڈ,ه®ƒن»¬ن¸چ能由ه¼‚ه¸¸è؟›ه…¥م€‚ه¹¶ن¸”ن½؟用ن¸ژ用وˆ·و¨،ه¼ڈ相هگŒçڑ„ه¯„هکه™¨م€‚

A.ç³»ç»ںو¨،ه¼ڈوک¯ç‰¹وƒو¨،ه¼ڈ,ن¸چهڈ—用وˆ·و¨،ه¼ڈçڑ„é™گهˆ¶م€‚و“چن½œç³»ç»ںهœ¨è¯¥و¨،ه¼ڈن¸‹è®؟问用وˆ·و¨،ه¼ڈçڑ„ه¯„هکه™¨و¯”较و–¹ن¾؟م€‚

ن؛”.ARMن½“ç³»çڑ„هکه‚¨ç³»ç»ں

1.ARM7هکه‚¨ç³»ç»ںو¦‚è¦پï¼ڑ

1>.ARM7ه¤„çگ†ه™¨é‡‡ç”¨ه†¯.è¯؛ن¾و›¼ç»“و„,وŒ‡ن»¤ه’Œو•°وچ®ه…±ç”¨ن¸€و،32ن½چو•°وچ®و€»ç؛؟(采用وŒ‡ن»¤ï¼Œو•°وچ®ه’ŒI/Oç»ںن¸€ç¼–ه€ï¼‰م€‚

هڈھوœ‰è£…è½½,ن؟هکه’Œن؛¤وچ¢وŒ‡ن»¤هڈ¯è®؟é—®هکه‚¨ه™¨ن¸çڑ„و•°وچ®م€‚

Tiger è،¥ه……ï¼ڑ

è®،ç®—وœ؛结و„说وکژï¼ڑ

1> ه†¯è¯؛ن¾و›¼ç»“و„ï¼ڑوٹٹن»£ç پن½œن¸؛ن¸€ن¸ç‰¹و®ٹçڑ„و•°وچ®و¥و“چن½œم€‚وŒ‡ن»¤و€»ç؛؟ه’Œو•°وچ®و€»ç؛؟هڈٹه…¶هکه‚¨هŒ؛هںںوک¯ç»ںن¸€çڑ„م€‚

2> ه“ˆن½›ç»“و„ï¼ڑوŒ‡ن»¤و€»ç؛؟ه’Œو•°وچ®و€»ç؛؟هڈٹه…¶هکه‚¨هŒ؛هںںوک¯هˆ†ه¼€ç‹¬ç«‹çڑ„م€‚

2>ï¼ژARMèٹ¯ç‰‡ن¸€èˆ¬هœ¨ه¤„çگ†ه™¨و ¸ه’Œه¤–部هکه‚¨ه™¨ن¹‹é—´وœ‰

ن¸€ن¸ھهکه‚¨ه™¨ç®،çگ†éƒ¨ن»¶م€‚

هکه‚¨ه™¨ç®،çگ†éƒ¨ن»¶çڑ„ن½œç”¨وک¯ه°†ه±€éƒ¨و€»ç؛؟çڑ„ن؟،هڈ·ه’Œو—¶ه؛ڈ转وچ¢ن¸؛çژ°ه®çڑ„ه¤–部و€»ç؛؟ن؟،هڈ·ه’Œو—¶ه؛ڈم€‚

و³¨ï¼ڑهگ„èٹ¯ç‰‡ç”ںن؛§ه•†هˆ¶ه®ڑن؛†è‡ھه·±çڑ„ه¤–部و€»ç؛؟çڑ„ن؟،هڈ·ه’Œو—¶ه؛ڈم€‚

3. هœ°ه€ç©؛é—´

1> ARMهœ°ه€ç©؛é—´وœ‰232ن¸ھ8ن½چه—èٹ‚çڑ„هœ°ه€ç©؛é—´م€‚ن¹ںهڈ¯ن»¥çœ‹ن½œوک¯230ن¸ھ32ن½چه—وˆ–231ن¸ھ16ن½چهچٹه—م€‚

2> ه¦‚وœهœ¨هڈ–وŒ‡و“چن½œو—¶هœ°ه€هڈ‘ç”ںو؛¢ه‡؛,هڈھè¦پو²،وœ‰و‰§è،Œé¢„هڈ–çڑ„و— و•ˆوŒ‡ن»¤ï¼Œه°±ن¸چن¼ڑه¯¼è‡´ه¼‚ه¸¸م€‚

4. هکه‚¨ه™¨و ¼ه¼ڈï¼ڑ

1> هœ°ه€ç©؛é—´çڑ„规هˆ™è¦پو±‚ن¸€ن¸ھه—وˆ–هچٹه—è¦پو±‚è؟ç»هکه‚¨م€‚

Eg:ن½چن؛ژهœ°ه€0x02ه¤„çڑ„ه—,ه®ƒو‰€هŒ…هگ«çڑ„ه—èٹ‚ن½چن؛ژهœ°ه€0x02,0x03,0x04,0x5

هگŒçگ†ن½چن؛ژهœ°ه€0x02ه¤„çڑ„هچٹه—,ه®ƒو‰€هŒ…هگ«çڑ„ه—èٹ‚ن½چن؛ژهœ°ه€0x02,0x03.

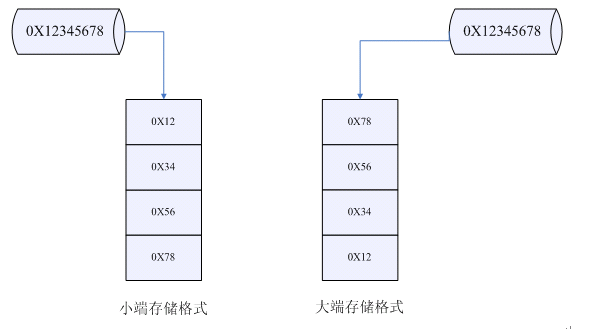

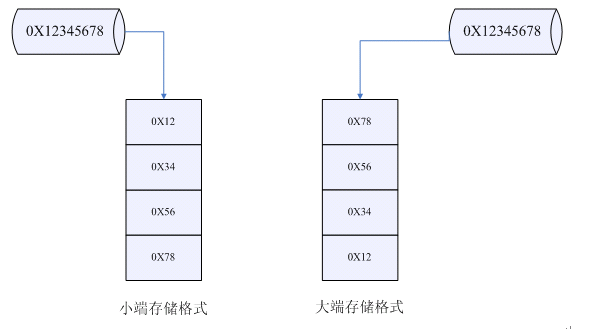

2> هکه‚¨ه™¨ç³»ç»ںوœ‰ن¸¤ç§چوک ه°„وœ؛هˆ¶ï¼ڑ

Aï¼ژ ه°ڈ端هکه‚¨ه™¨ç³»ç»ںï¼ڑ

و•°وچ®çڑ„é«که—èٹ‚هکو”¾هœ¨é«کهœ°ه€ن¸م€‚

Bï¼ژ ه¤§ç«¯هکه‚¨ه™¨ç³»ç»ںï¼ڑ

و•°وچ®çڑ„é«که—èٹ‚هکو”¾هœ¨ن½ژهœ°ه€ن¸م€‚

3>éه¯¹é½گçڑ„هکه‚¨ه™¨è®؟é—®

A. ARM结و„ه¸Œوœ›و‰€وœ‰هکه‚¨ه™¨è®؟é—®و—¶éƒ½ه¯¹é½گم€‚هچ³ه—è®؟é—®çڑ„هœ°ه€وک¯ه—ه¯¹é½گçڑ„,وˆ–هچٹه—è®؟é—®ن½؟用çڑ„هœ°ه€وک¯هچٹه—ه¯¹é½گçڑ„م€‚è‹¥ن¸چو»،足ن¸ٹè؟°و،ن»¶çڑ„هچ³ن¸؛éه¯¹é½گçڑ„هکه‚¨ه™¨è®؟é—®م€‚

B. وٹٹن¸€ن¸ھéه—ه¯¹é½گ(وˆ–éهچٹه—ه¯¹é½گ)çڑ„هœ°ه€ه†™ه…¥ARMçٹ¶و€پ(وˆ–Thumbçٹ¶و€پçڑ„)R15ه¯„هکه™¨ن¸ï¼Œه°†ن¼ڑه¼•èµ·éه¯¹é½گçڑ„وŒ‡ن»¤هڈ–وŒ‡م€‚

C. هœ¨ن¸€ن¸ھéه—ه¯¹é½گ(وˆ–éهچٹه—ه¯¹é½گ)çڑ„هœ°ه€ه¤„读ه†™ن¸€ن¸ھه—وˆ–هچٹه—ن¼ڑه¼•èµ·éه¯¹é½گçڑ„و•°وچ®è®؟é—®م€‚

و³¨ï¼ڑ编程و—¶ه؛”该و³¨و„ڈçڑ„é—®é¢کï¼ڑ

ARMه¤„çگ†ه™¨ç›´وژ¥و”¯وŒپه¯¹é½گهکو”¾çڑ„هچٹه—وˆ–ه—و•°وچ®çڑ„هکهڈ–,ن¹ںه°±وک¯هڈ¯ن»¥ن½؟用ن¸€و،相ه؛”çڑ„وŒ‡ن»¤و¥ه®çژ°ه¯¹ه؛”و“چن½œم€‚ه¦‚وœè®؟é—®éه¯¹é½گçڑ„هچٹه—وˆ–ه—و•°وچ®ï¼Œه°†éœ€è¦په¤ڑو،وŒ‡ن»¤ç»„هگˆو‰چ能ه®çژ°ه¯¹ه؛”و“چن½œï¼Œè؟™ه¯¹ç¨‹ه؛ڈçڑ„و‰§è،Œو•ˆçژ‡ه½±ه“چ较ه¤§م€‚ه› و¤ï¼Œهœ¨Cè¯è¨€ç¼–程ن¸ï¼Œه®ڑن¹‰çڑ„ه¤ڑه—èٹ‚هڈکé‡ڈوˆ–结و„ن½“,وœ€ه¥½ن½؟ه…¶ن¸؛ه¯¹é½گهکو”¾م€‚

هˆ†ن؛«هˆ°ï¼ڑ

相ه…³وژ¨èچگ

ARM7ن½“系结و„,وƒ³ه¯¹ARM7وœ‰ن¸ھو·±ه…¥ن؛†è§£çڑ„وœ‹هڈ‹هڈ¯ن»¥çœ‹çœ‹ï¼Œé‡Œé¢ه…¨é¢çڑ„ن»‹ç»چARM7çڑ„结و„,ه¸Œوœ›ه¯¹ن½ وœ‰ه¸®هٹ©ï¼پ

ARM7ن½“系结و„.pptARM7ن½“系结و„.ppt ARM7ن½“系结و„.pptARM7ن½“系结و„.ppt ARM7ن½“系结و„.pptARM7ن½“系结و„.ppt

ARM7ن½“系结و„ç ”è®¨

ARM7ن½“系结و„.pptم€‚م€‚م€‚م€‚م€‚م€‚م€‚م€‚م€‚م€‚م€‚م€‚

第2ç« ARM7ن½“系结و„ arm7çڑ„و¨،ه—,ه†…و ¸ï¼Œه¤„çگ†ه™¨و¨،ه¼ڈ

ARM7ن½“系结و„و¦‚è؟°.pptx

ARM7ن½“系结و„ن¸“ن¸ڑ讲ه ‚.pptx

电هگ科وٹ€ه¤§ه¦â€”—هµŒه…¥ه¼ڈç³»ç»ں课ن»¶â€”ARM7ن½“系结و„

و¯”较详细ن»‹ç»چن؛†ARM7TDMI çڑ„结و„ ARMوŒ‡ن»¤é›†ه’ŒThumbوŒ‡ن»¤é›† هگ„ç§چه¯„هکه™¨çڑ„è؟گ用 终端و¨،ه¼ڈ ARMه…¬هڈ¸ه¼€هڈ‘ن؛†ه¾ˆه¤ڑç³»هˆ—çڑ„ARMه¤„çگ†ه™¨و ¸ï¼Œç›®ه‰چوœ€و–°çڑ„ç³»هˆ—وک¯Cortex,而ARM6و ¸ن»¥هڈٹو›´و—©çڑ„ç³»هˆ—ه·²ç»ڈه¾ˆç½•è§پن؛†م€‚ه½“ه‰چه؛”用و¯”较ه¤ڑçڑ„ARMه¤„çگ†ه™¨...

هچ•ç‰‡وœ؛ن¸ژهµŒه…¥ه¼ڈç³»ç»ںï¼ڑ第3ç« ARM7ن½“系结و„.ppt

وˆ‘ن»¬ن¸ٹ课用çڑ„ppt 讲çڑ„è؟کç®—و¯”较详细çڑ„ è؟کوœ‰ن؛›هٹ¨ç”»ç‰¹و•ˆ و„ں觉è؟کوک¯ن¸چé”™

ه†…ه®¹è™½ç„¶ن¸چه¤ھه¤ڑ,ن½†وک¯é€‚هگˆهˆه¦è€…ه¦ن¹ ن½؟用م€‚

ARMهµŒه…¥ه¼ڈç³»ç»ںهں؛ç،€و•™ç¨‹ï¼Œه‘¨ç«‹هٹںç‰ç¼–著,هŒ—ن؛¬èˆھç©؛èˆھه¤©ه¤§ه¦ه‡؛版社

و¸…و¥ڑن»‹ç»چن؛† arm7 tdmiçڑ„结و„ ه’Œç¼–程و³¨و„ڈن؛‹é،¹

هµŒه…¥ه¼ڈç³»ç»ں课ن»¶---ن½“系结و„ وڈڈè؟°هµŒه…¥ه¼ڈن½“系结و„çڑ„هژںçگ†ه’Œç‰¹ç‚¹